# Драйверы для обеспечения взаимодействия ускорителя с реконфигурируемой архитектурой и центрального процессора вычислительной системы.

#### Организация взаимодействия ПЛИС с ПК

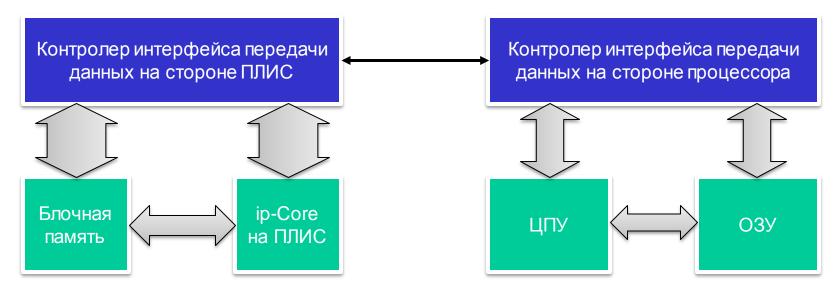

- ір-Ядра в ПЛИС не могут быть вызваны из ЦПУ непосредственно даже, если находятся на одном кристалле, поскольку имеют отличную архитектуру.

- Взаимодействие происходит через контроллеры посредники по специальному протоколу.

- Пропускная способность интерфейса передачи данных существенно ниже пропускной способности внутренних интерфейсов реализованных в ПЛИС.

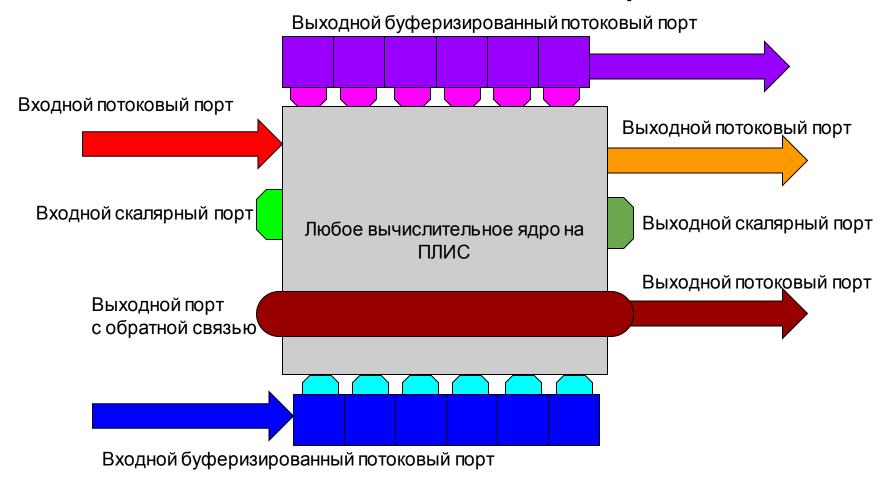

#### Вычислительное ядро

#### Оптимизация передачи данных

```

int i;

for (i = 0; i < 1000; ++i) {

a[i] = (b[2*i] + b[2*i + 1])*c[i];

}</pre>

```

| i | 0          | 1          | 2          | 3          |

|---|------------|------------|------------|------------|

| b | b[0]; b[1] | b[2]; b[3] | b[4]; b[5] | b[6]; b[7] |

| С | -          | c[0]       | c[1]       | c[2]       |

| а | -          | -          | a[0]       | a[1]       |

```

for (i = 0; i < 1000; ++i) {

a[i] = (b[i] + b[i + 2])*c[i];

}</pre>

```

| i | 0          | 1          | 2          | 3          |

|---|------------|------------|------------|------------|

| b | b[0]; b[2] | b[1]; b[3] | b[2]; b[4] | b[3]; b[5] |

| С | -          | c[0]       | c[1]       | c[2]       |

| а | -          | -          | a[0]       | a[1]       |

#### Задачи драйвера

- 1. Управление вычислительными ядрами на ПЛИС.

- 2. Преобразование форматов хранения данных.

- 3. Буферизация отправляемых и получаемых данных.

- 4. Оптимизация порядка передачи данных.

- 5. Синхронизация потоков данных.

- 6. Синхронизация вычислительных потоков.

#### Алгоритм работы драйвера

- 1. Конфигурация ядра. Отправка конфигурационных данных на порты-константы и буферизированные потоковые порты.

- 2. Инициализация ядра. Отправка начальных значений на порты с обратной связью и буферизированные потоковые порты с обратной связью.

- 3. Работа ядра. Отправка данных на потоковые порты и одновременное получение результатов с потоковых выходных портов.

- 4. Де-инициализация. Получение данных с буферизированных потоковых портов и скалярных портов.

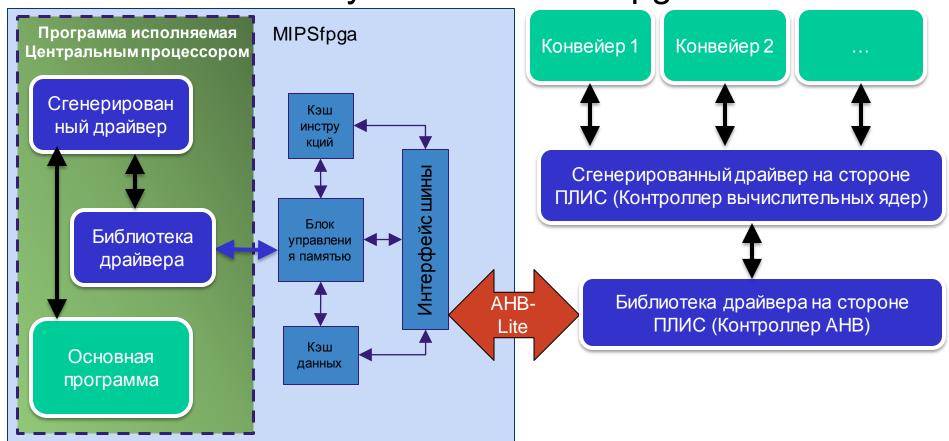

## Разделение драйвера на статическую и генерируемую части

- Функционал, который может зависеть от структуры конкретной программы.

- о Порядок отправки и получения данных.

- о Функция конфигурирования вычислительного ядра.

- о Функция инициализации вычислительного ядра.

- Функционал, который зависит только от выбранного интерфейса передачи данных и целевой платформы.

- Функции обмена данными между ЦПУ и ПЛИС.

- Буферы для отправляемых и получаемых данных на ПЛИС.

### Проект компилятора на вычислительную систему с реконфигурируемой архитектурой

- Блок высокоуровневых преобразований. Находит в программе конвейеризуемые участки, а так же применяет преобразования, если те необходимы, способные улучшить конвейеризуемость кода.

- Преобразователь С в VHDL (C2HDL). Конвейеризация циклов и преобразование части кода исходной программы в описание вычислительного ядра на языке VHDL.

- Генератор драйверов. Автоматическая генерация на Си и VHDL вспомогательных модулей, обеспечивающих взаимодействие ПК и ПЛИС.

- Менеджер сборки. Из всех сгенерированных файлов собирает два проекта на Си и на VHDL соответственно, с описанием параметров компиляции каждого проекта. Также управляет процессом компиляции исходного кода в исполняемые файлы целевых платформ.

Экспериментальный стенд на базе Altera Cyclone V и MIPSfpga